)

(2

.

Experiment No

logic Gates

:

Objective

To

study

(

NAND, NOR, AND, OR, NOT, X-OR, X-NOR)

Gates

and

to

realize

the Boolean

equation

for

the

Gates

Introduction:

Logic Gates:

Logic gate is an electronic circuit manufactured mainly as integrated

circuit

(IC)

unit

by

employing

transistors,

diodes,

and

other

solid

state

components.

The

Primary

Logic

gates

(AND ,

OR

and

NOT )

are

used

to

implement

different

Boolean

equations

as

well

as

the

constructing

of

other

logic

gates.

Logic

gates

have

one

or

more

input

terminals

and

only

one

output

terminal.

33002

-

Module

KL

Equipments required

:

Procedures

(a) NAND Gate (Module KL-33002 block b)

1.

Module

KL-33002

block

b

will

be

used

in

this

section.

2. Connect the inputs

(A,

A1)

to

data

switch

SW0,

SW1

on

the TTL

level.

3

.

Connect

the

output

F2

to

the

logic

indicator

L0,

then

follow

the

input

sequences

in

table

(1-1) to

record

the

output

.

KL-31001 Base unit

Table(1-1)

INPUT

OUTPUT

SW1(A1) SW0(A)

F2

0

0

0

1

1

0

1

1

(b)

NOR

Gate

(Module

KL-33002

block

a)

1.

Module

KL-33002

block

a

will

be

used

in

this

section.

2.

Connect

the

inputs

A1,

B1

to

the

data

switch

SW0, SW1

on

the

TTL

level.

3. Connect the output F3 to the logic indicator L0, then follow the input sequences in

table(1-2)

to

record

the

output

F3.

Table(1-2)

INPUT

OUTPUT

SW1(A1) SW0(B1)

F3

0

0

0

1

1

0

1

1

(c). NOT Gate (Module KL-33002 block c)

1. U4c of Module KL-33002 block c will be used in this section.

2. Connect input F3 and output F4 of U3c to SW0 and L0 respectively. Follow

the input sequences in table(1-3) and record outputs.

Table(1-3)

INPUT

OUTPUT

F4

0

1

SW0(F3)

(d) AND Gate (Module KL-33002 block b & c)

1. Block b and c of module KL-33002 will be used in this section.

2. Connect the

inputs A, A1 (block b) to the

data

switch

SW0,

SW1

on

the

TTL

level.

3

. Connect the output F2 (block b) to the Not gate input F3 (block c). Then connect the

output F4 (block c) to logic indicator L0, then follow the input sequences in table (1-4) to

record the output.

Table(1-4)

INPUT

OUTPUT

SW1(A1) SW0(A)

F4

0

0

0

1

1

0

1

1

(e) OR Gate (Module KL-33002 block

a & c

)

1. block

a

and

c of

module

KL-33002 will be used in this section.

2. Connect the inputs A1, B1 (block

a)

to data switch SW0, SW1 on the TTL level.

3.

Connect

the

output

F3

(block

a)

to

the

Not

gate

input

F3

(block

c).

Then

connect

the

output

F4

(block

c)

to

logic

indicator

L0,

then

follow

the

input

sequences

in

table

(1-5)

to

record

the

output.

Table(1-5)

INPUT

OUTPUT

SW1(A1) SW0(B1)

F4

0

0

0

1

1

0

1

1

(f) XOR Gate (Module KL-33002 block c)

1. block c of module KL-33002 will be used in this section.

2. Connect the inputs A, B (block c) to data switch SW0, SW1 on the TTL level.

3.

Connect the output F5 to logic indicator L0, then follow the input sequences in

table (1-6) to record the output.

Table(1-6)

INPUT

OUTPUT

SW1(A) SW0(B)

F5

0

0

0

1

1

0

1

1

(g) X-NOR Gate (Module KL-33002 block

c

)

1. block c of module KL-33002 will be used in this section.

2. Connect the inputs A, B (block c) to data switch SW0, SW1 on the TTL level.

3. Connect the output F5 to the Not gate input F3. Then connect the output F4 to

logic indicator L0, then follow the input sequences in table (1-7) to record the output.

Table(1-7)

INPUT

OUTPUT

SW1(A1) SW0(B1)

F4

0

0

0

1

1

0

1

1

:

Discussion

1. What is a logic gate?

2. When does the AND

gate produce

a

high

output?

3. When does the OR gate

produce

a

low

output?

4. List one

application for using X-OR gate.

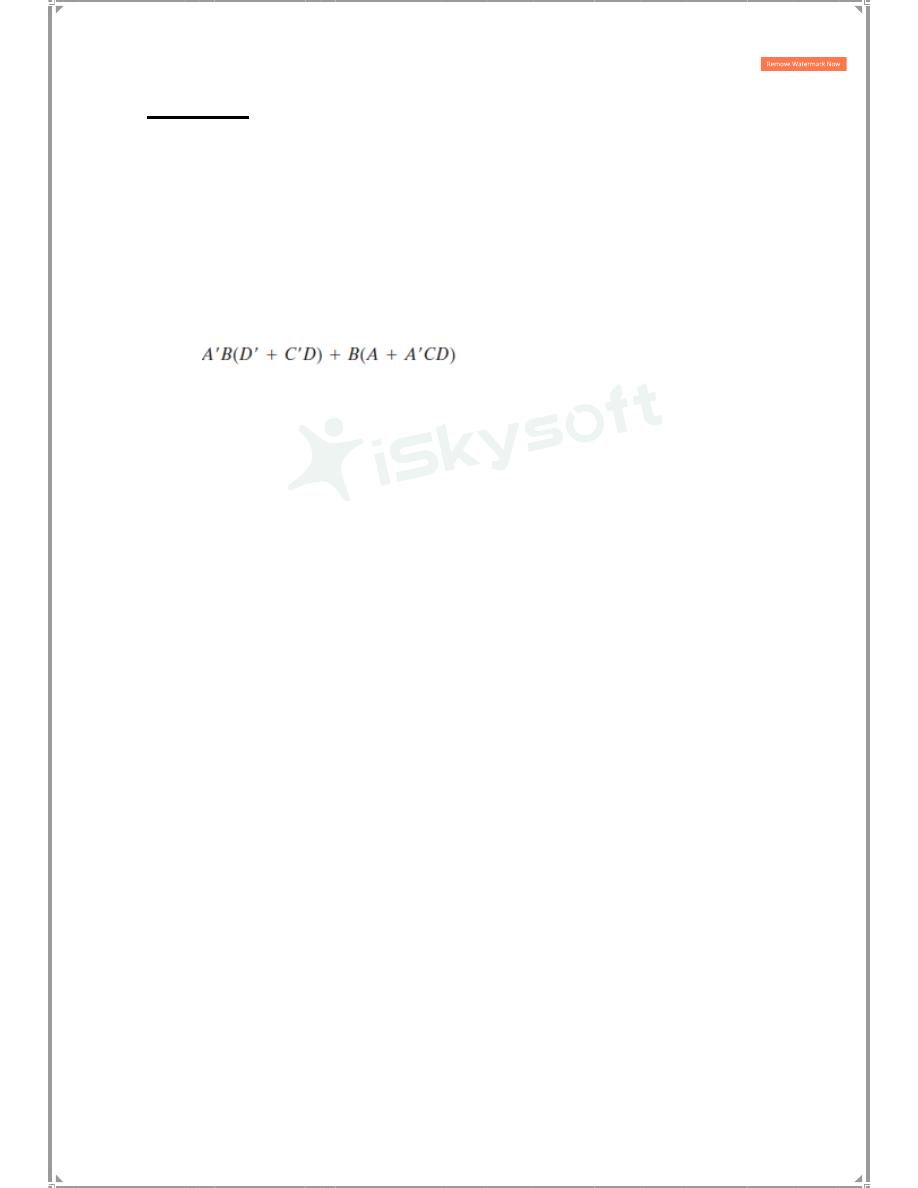

5. Design a logical

circuit

that

satisfies

the

following

equation

before and after

simplifying

it

6. Design a 5-input OR gate by using 2-input OR gates?