ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٢٦

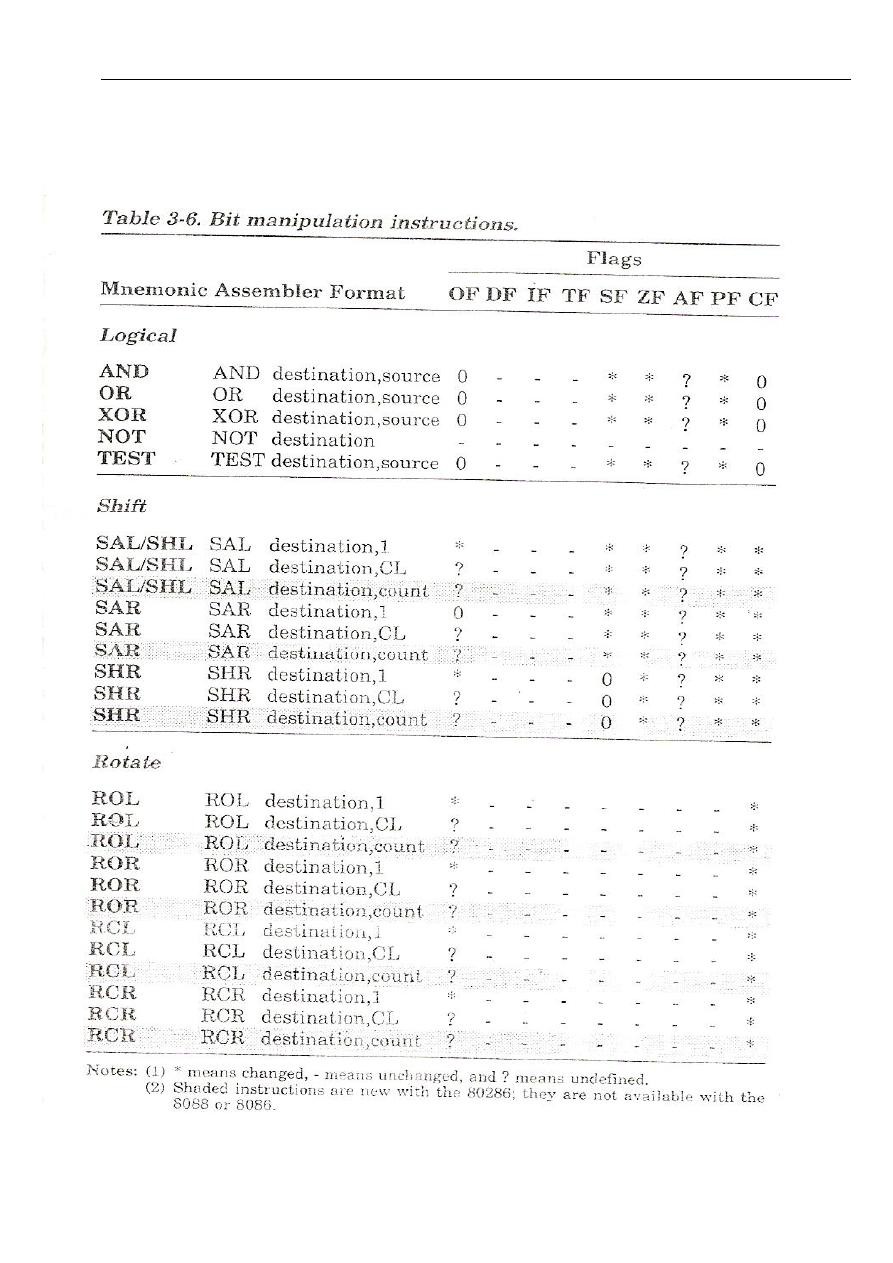

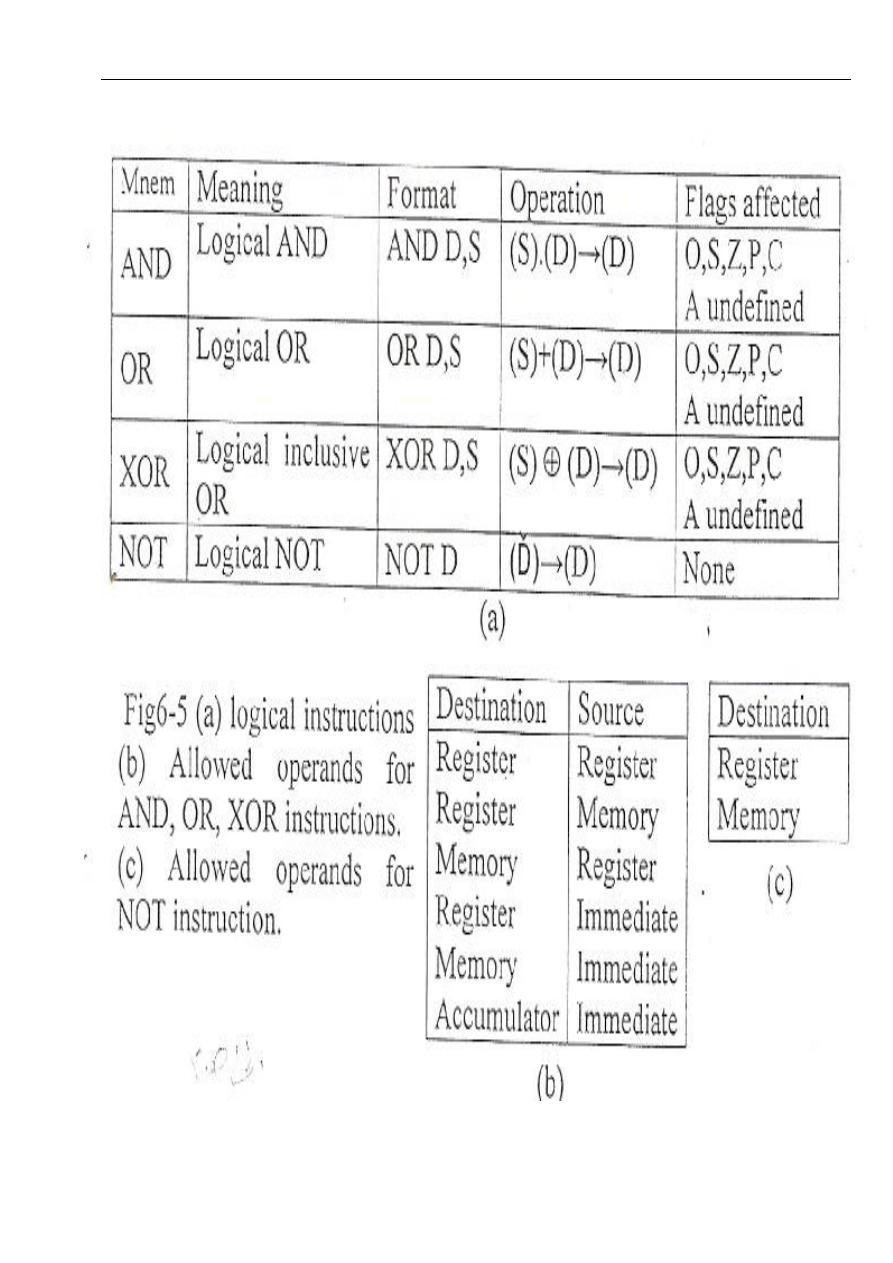

BIT MANIPULATION INSTRUCTIONS

These instructions manipulate bit patterns within registers and memory locations .Table 1

divides them into three groups: logical, shift and rotate.

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٣٦

Logical Instructions

Logical instructions are so named because they operate according to the rules of

formal logic, rather than those of mathematics. For example, the rule of logic that

states, "If A is true and B is true, then C is true" have the same operate as AND

instruction. AND applies this rule to corresponding bits in two operands.

، ﻴﺔـﻀﺎﻴﺭﻟﺍ ﻥﻴﻨﺍﻭـﻘﻟﺍ ﻥـﻤ ﻻﺩـﺒ ﺔـﻴﻘﻁﻨﻤﻟﺍ ﻥﻴﻨﺍﻭـﻘﻟﺍ ﻕـﻓﻭ لـﻤﻌﺘ ﺎﻬﻨﻻ ﻴﺔﻘﻁﻨﻤﻟﺍ ﺕﺍﺯﺎﻌﻴﻻﺎﺒ ﺕﺍﺯﺎﻌﻴﻻﺍ ﻩﺫﻫ ﻰﻤﺴﺘ

ﺎﻥـﻜ ﺍﺫﺍ ﻪـﻨﺍ ﻰـﻠﻋ ﺹﻨﻴ ﻱﺫﻟﺍ ﻲﻘﻁﻨﻤﻟﺍ ﻥﻭﻨﺎﻘﻟﺍ ﺎﻥﻓ لﺎﺜﻤﻜﻭ

A is true

ﻭ

B is true

ﻭـﻫ ﺞﺘﺎـﻨﻟﺍ ﻥﺎـﻓ

C is true

ﻫﻭ ﻴﻤﺎﺜل ﻋﻤل ﺍﻴﻌﺎﺯ

AND

ﻭﻴﻘﻭﻡ ﺍﻴﻌﺎﺯ،

AND

ﺒﺘ

ﻁﺒﻴﻕ ﻋﻠﻰ ﺍﻟﺒﺘﺎﺕ ﺍﻟﺨﺎﺼﺔ ﺒﺎﻟﺒﻴﺎﻨﺎﺕ ﺍﻟﺘﻲ ﻴﻌﻤل ﻋﻠﻴﻬﺎ

.

Specifically, for each bit position where both operands are 1 (true), AND sets the

corresponding bit in the destination operand to 1. Conversely, for any bit position

where the two operands Rave any other combination—both are 0 or one is 0 and the

other is 1 AND sets the bit in the destination to 0.

ﻮ"""ھ ﺎ"""ﻤھﻼﻛ نﺎ"""ﻛ اذا ﻦﯿ"""ﺘﺒﻠﻟ ﻊ"""ﻗﻮﻣ نﺎ"""ﻓ ، سﺎ"""ﺳﻻا اﺬ"""ھ ﻰ"""ﻠﻋو

1(true)

ﺎن"""ﻓ

AND

ﺖ"""ﺒﻟا ﻊ"""ﻗﻮﻤﺑ ﺪ"""ﺣاو ﺔ"""ﻤﯿﻗ ﻊ"""ﻀﯾ

ﺘﻘﺮ""""ﺴﻤﻟا ﻲ""""ﻓ ﺮﻇﺎ""""ﻨﻤﻟا

.

ﻦ""""ﻋ ﺔ""""ﻠﻔﺘﺨﻣ ﻢﯿ""""ﻘﺑو ﻦﯿﯾﺮ""""ﺧا ﻦﯿ""""ﺘﺑ ﻊ""""ﻗﻮﻣ يﻻ ﻲﻟﺎ""""ﺘﻟﺎﺑو

ﺎ""""ﻤﮭﯿﻨﺛا نﻮ""""ﻜﺗ نﺎ""""ﻛ ﻰ""""ﻟوﻻا ﺔ""""ﻟﺎﺤﻟا

0

اواﺣﺪھﻤﺎ

0

واﻻﺧﺮ

1

ﺑﻐﺾ اﻟﻨﻈﺮ

ﻋﻦ اﻟﺘﺮﺗﯿﺐ ﻓﺎن اﻟﻨﺎﺗﺞ اﻟﺬي ﯾﻀﻌﮫ

AND

ﻓﻲ ﺑﺖ اﻟﻤﺴﺘﻘﺮ ھﻮ

0

.

Since logical operations reference bits within an operand, we generally use

hexadecimal numbering for the operands. The logical instructions can operate on

either bytes or words, so you normally deal with either two or four hexadecimal

digits.

ﺎﻡـﻗﺭﻻﺍ ﻰـﻠﻋ لـﻤﻌﻨ ﺎﻡـﻋ لﻜـﺸﺒ ﺎـﻨﻨﺎﻓ ، ﺕﺎـﻨﺎﻴﺒﻟﺍ ﺕﻼﻤﺎـﻌﻤ ﻥﻤﻀ ﺕﺎﺘﺒﻟﺍ ﻰﻠﻋ لﻤﻌﺘ ﺔﻴﻘﻁﻨﻤﻟﺍ ﺕﺎﻴﻠﻤﻌﻟﺍ ﻥﺍ ﺎﻤﺒ

ﺎﺕـﻨﺎﻴﺒﻟﺍ ﺕﻼﻤﺎﻌﻤﻟ ﺔﺒﺴﻨﻟﺎﺒ ﺔﻴﺭﺸﻋ ﺱﺩﺎﺴﻟﺍ ﺔﻐﻴﺼﻟﺎﺒ

.

ـﻭﺘﺴ

ﺕ ﺍﻭـﻴﺎﺒﻟﺍ ﻰـﻠﻋ لـﻤﻌﺘ ﻥﺍ ﺔـﻴﻘﻁﻨﻤﻟﺍ ﺕﺍﺯﺎـﻌﻴﻻﺍ ﻊﻴﻁﺘ

ﺍﻟﻜﻠﻤﺔ ﻭﻟﺫﻟﻙ ﻓﺎﻨﻨﺎ ﻨﺘﻌﺎﻤل ﻤﻊ ﺭﻗﻤﻴﻥ ﺍﻭ ﺍﺭﺒﻌﺔ ﺍﺭﻗﺎﻡ ﺒﺎﻟﺼﻴﻐﺔ ﺍﻟﺴﺎﺩﺱ ﻋﺸﺭﻴﺔ

.

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٤٦

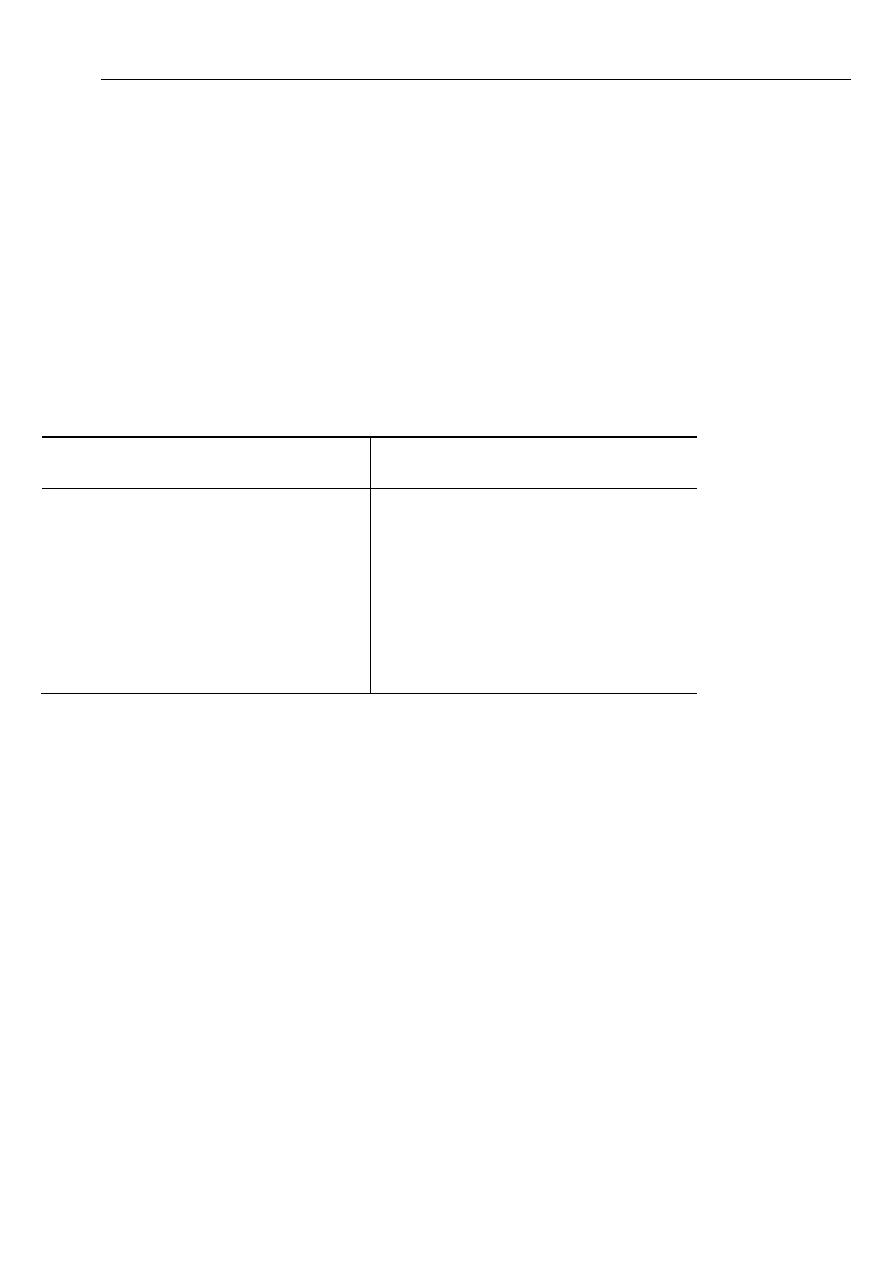

We can construct the correct "mask" value for a logical operation by using Table 2

which shows the hexadecimal representation of a 1 in 16 different bit positions. For

example, to operate on bit 2, the correct mask value is 4H; to operate on bits 2 and 3,

the mask is 0CH (hex 4 + hex 8); and so on

ﺐ"""ﺠﺤﻟا اﺪ"""ﺒﻣ ءﺎ"""ﻨﺒﺑ مﻮﻘﻨ"""ﺳو

mask

ﻢ"""ﻗر لوﺪ"""ﺠﻟا ماﺪﺨﺘ"""ﺳا لﻼ"""ﺧ ﻦ"""ﻣ ﺔ"""ﯿﻘﻄﻨﻤﻟا تﺎ"""ﯿﻠﻤﻌﻟا ﻦﻤ"""ﺿ ﺢﯿﺤ"""ﺻ ﻞﻜ"""ﺸﺑ

٢

ﺬي"""ﻟاو

ﻞ اﻟ"""ﯿﺜﻤﺘﻟا ﺎ"""ﻨﻟ ﻦﯿ"""ﺒﯾ

ﺎدس"""ﺴ

ﺮي"""ﺸﻋ

ﺎﻧﻲ"""ﺜﻟا ﺖ"""ﺒﻟا ﻊ"""ﻣ ﻞ"""ﻤﻌﻠﻠﻓ لﺎ"""ﺜﻤﻛو ﺮ"""ﺸﻋ سدﺎ"""ﺴﻟا ﻰ"""ﻟا لوﻻا ﺖ"""ﺒﻟا ﻦ"""ﻣ تﺎ"""ﺘﺒﻟا ﻊ"""ﻗاﻮﻤﻟ

ﺔ"""ﻤﯿﻗ نﺎ"""ﻓ

mask

ﻲ"""ھ ﺔﺤﯿﺤ"""ﺼﻟا

4H

ﺔ"""ﻤﯿﻗ نﺎ"""ﻓ ﺚ"""ﻟﺎﺜﻟاو ﻲﻧﺎ"""ﺜﻟا ﻦﯿ"""ﺘﺒﻟا ﻰ"""ﻠﻋ ﻞ"""ﻤﻌﻠﻟو ،

mask

ﻲ"""ھ ﺔﺤﯿﺤ"""ﺼﻟا

0C

(hex 4 + hex 8)

وھﻜﺬا

Table 2, Hexadecimal values for bit positions

.

Bit Number

Hex. Value

Bit Number

Hex. Value

0

0001

8

0100

1

0002

9

0200

2

0004

10

0400

3

0008

11

0800

4

0010

12

1000

5

0020

13

2000

6

0040

14

4000

7

0080

15

8000

Logical AND (AND), Inclusive-OR (OR), and Exclusive-OR (XOR)

AND, OR, and XOR operate on byte or word operands. They let combine two

registers, a register with a memory location, or an immediate value with a register or

memory location. Table 3 shows what effect these instructions have.

ﺎزات"""ﻌﯾﻻا

AND, OR, and XOR

ﻤﺢ"""ﺴﺗ ﻲ"""ھو ، تﺎ"""ﻤﻠﻜﻟا وا ﺖ"""ﯾﺎﺒﻟا ﺔ"""ﯿﻋﻮﻧ ﻦ"""ﻣ تﺎ"""ﻧﺎﯿﺒﻟا تﻼﻣﺎ"""ﻌﻣ ﻰ"""ﻠﻋ ﻞ"""ﻤﻌﺗ

ﺮة"""ﻛاذ ﻊ"""ﻗﻮﻣ وا ﻞﺠ"""ﺴﻣ ﻊ"""ﻣ ﺮة"""ﺷﺎﺒﻣ ﺔ"""ﻤﯿﻘﺑ وا ﺮة"""ﻛاذ ﻊ"""ﻗﻮﻣ ﻊ"""ﻣ ﻞﺠ"""ﺴﻣ وا ﻦﯿﻠﺠ"""ﺴﻣ ﻊ"""ﻣ ﻞ"""ﻤﻌﻟﺎﺑ

.

ﺔ"""ﯿﻔﯿﻛ لوﺪ"""ﺠﻟا ﻦﯿ"""ﺒﯾو

ﺗﺎﺛﯿﺮ ھﺬه اﻻﯾﻌﺎزات ﻋﻠﻰ ﻣﻌﺎﻣﻼت اﻟﺒﯿﺎﻧﺎت

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٥٦

Table 3. AND, OR, and XOR bit combinations.

Source

Destination

AND

OR

XOR

0

0

0

0

0

0

1

0

1

1

1

0

0

1

1

1

1

1

1

0

The AND instruction masks out (zeroes) certain bits so you can do some kind of

processing on the remaining bits. As we just mentioned, for each bit position in which

both operands contain 1, the corresponding bit in the destination is also 1. All other

operand bit combinations put a 0 in the destination bit. Note that any bit ANDed with

0 becomes 0, and any bit ANDed with 1 retains its original value.

ﺎز""""ﻌﯾا مﻮ""""ﻘﯾ

AND

ﻞ""""ﻤﻌﺑ

masks

ﺎت""""ﺘﺒﻟا ﻰ""""ﻠﻋ ﺔ""""ﺠﻟﺎﻌﻣ يا ﻞ""""ﻤﻋ ﻦ""""ﻜﻤﯾ ﺚ""""ﯿﺤﺑو رﺎﻔ""""ﺻا ﺔ""""ﻨﯿﻌﻣ ﺎت""""ﺘﺑ ﻞ""""ﻌﺠﯾ يا

ﯿﺤﮫ""ﺿﻮﺗ ﻢ""ﺗ ﺎ""ﻤﻛو ﺔ""ﯿﻗﺎﺒﻟا

ﺎﺑﻘﺎ""ﺳ

ﺎن""ﻓ

ﺘﻘﺮ""ﺴﻤﻟا ﻲ""ﻓ ﺮﻇﺎ""ﻨﻤﻟا ﺖ""ﺒﻟا نﺎ""ﻓ ﺪ""ﺣاو ﺎ""ﻤﮭﻟ ﻦﯿ""ﻨﺛﻻا تﺎ""ﻧﺎﯿﺒﻟا ﻢﯿ""ﻗ نﻮ""ﻜﯾ ﻊ""ﻗﻮﻣ يا

"""ﺐ ﻣﻼﺣﻈ"""ﺠﯾو ﺮﻘﺘ"""ﺴﻤﻟا ﺖ"""ﺑ ﻲ"""ﻓ ﺮﻔ"""ﺻ ﻊ"""ﻀﺗ ىﺮ"""ﺧﻻا تﻼﯿﻜ"""ﺸﺘﻟا ﻞ"""ﻛو ﺪ"""ﺣاو نﻮﻜﯿ"""ﺳ

ﮫ"""ﻟ ﻞ"""ﻤﻌﯾ ﺖ"""ﺑ يا ﮫ"""ﻧا ﺔ

AND

ﻣﻊ

0

ﯾﺼﺒﺢ

0

واي ﺑﺖ ﯾﻌﻤﻞ ﻟﮫ

AND

ﻣﻊ

1

ﻓﺎﻧﮫ ﯾﺤﺘﻔﻆ ﺑﻘﯿﻤﺘﮫ اﻻﺻﻠﯿﺔ

.

Some examples of AND are:

AND AX, BX ; AND two registers

AND AL,MEM_BITE ; AND register with memory

AND MEM_BYIE, AL

; or vice versa

AND BL,11111101B

; AND a constant with a register

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٦٦

To see how AND works, suppose port 200 is connected to the 16-bit status register

of an external device in the system, and bit 6 indicates whether that device is on (1) or

off (0). If your program requires the device to be on before continuing, it might

include the following loop:

ﻞ"""ﻤﻌﯾ ﻒ"""ﯿﻛ ىﺮ"""ﻧ ﻲ"""ﻜﻟو

AND

ﺮض"""ﺘﻔﻨﻟ ،

ﺪﺧﻞ"""ﻤﻟا ﺎ"""ﻨﻤﻗ ﺎ"""ﻨﻧا

200

ﺔ ذو"""ﻟﺎﺤﻟا ﻞﺠ"""ﺴﻣ ﻰ"""ﻟا

16 bit

ﺎ"""ﺧ زﺎ"""ﮭﺠﻟ

ر

ﺟﻲ

ﺖ""""ﺒﻟاو ، مﺎ""""ﻈﻨﻟا ﻲ""""ﻓ

6

ﻞ""""ﻤﻌﯾ زﺎ""""ﮭﺠﻟا نا ﻦﯿ""""ﺒﯾ

1

ا

ﻞ""""ﻤﻌﯾﻻ زﺎ""""ﮭﺠﻟا و

0

ﺎن""""ﻛ اذاو

ﺎﻣﺞ""""ﻧﺮﺒﻟا

ﻮن""""ﻜﯾ نا جﺎ""""ﺘﺤﯾ زﺎ""""ﮭﺠﻟا

ﺷﻐﺎل ﺣﺘﻰ ﯾﺴﺘﻤﺮ ﻓﯿﺠﺐ ان ﯾﺘﻀﻤﻦ اﻟﺤﻠﻘﺔ اﻟﺘﻜﺮارﯾﺔ اﻟﺘﺎﻟﯿﺔ

:

CHK_PWR: IN AX , 200

; Read device status

AND AX, 1000000B ; Isolate the power indicator

JZ CHK_PWR

;Wait until power is on,

.. ;then continue

The JZ (Jump If Zero) instruction, which we have not yet discussed, makes the

jump back to the IN instruction at CHR_PWR if the Zero Flag (ZF) is 1, or continue

to the next instruction otherwise. Here, ZF is 1 only when the power indicator bit 6 is

0, because the AND instruction already zeroed the rest of the bits in AX.

ﺎز"""ﻌﯾا نا

JZ

ﻰ"""ﻟا ﺰ"""ﻔﻘﯾ ﺞﻣﺎ"""ﻧﺮﺒﻟا ﻞ"""ﻌﺠﯾ فﻮ"""ﺳ ﺎ"""ﻘﺣﻻ حﺮ"""ﺸﯿﺳ يﺬ"""ﻟاو ﺮﻔ"""ﺻ ﻮ"""ھ ﺞﺗﺎ"""ﻨﻟا نﺎ"""ﻛ اذا ﺰ"""ﻔﻗا ﻲ"""ﻨﻌﯾ يﺬ"""ﻟاو

ﺎز""""ﻌﯾا

IN

ﻄﺔ""""ﺳاﻮﺑ

label

ﺪد ب""""ﺤﻤﻟا

(CHR_PWR)

ﺎن""""ﻛ اذا

Zero Flag (ZF)

ﮫ""""ﻧﺎﻓ ﻻاو ، ﺪ""""ﺣاو ﮫ""""ﺘﻤﯿﻗ

ﺔ"""ﻤﯿﻗ ﺎ"""ﻨھ و مدﺎ"""ﻘﻟا زﺎ"""ﻌﯾﻻا ﻰ"""ﻟا ﺮﻤﺘ"""ﺴﯾ

ZF

ﺘﻜﻮن"""ﺳ

1

ﺎن"""ﻛ اذا ﻂ"""ﻘﻓ

bit 6

ﺎﻗﻲ"""ﺑ ﻦ"""ﻋ ﺮ"""ﻈﻨﻟا ﺾ"""ﻏ ﻢﺘ"""ﯾو ﺮﻔ"""ﺻ ﻮ"""ھ

اﻟﺒﺘﺎت ﻻﻧﮫ ﺗﻢ ﺗﺼﻔﯿﺮھﺎ ﻣﻦ ﺧﻼل ﻋﻤﻠﯿﺔ

AND

Note

We have two instructions Input and Output which are

IN AX , Input port number

Out Output port number, AX

ﻣﻼﺣﻈﺔ

ﻟﺪﯾﻨﺎ اﺛﻨﯿﻦ ﻣﻦ اﯾﻌﺎزات اﻻدﺧﺎل واﻻﺧﺮاج

The port number may be a port is connected to input device or output device.

ورﻗﻢ

port

ﻗﺪ ﯾﻜﻮن ل

port

ﻣﺮﺑﻮط ﺑﺠﮭﺎز ادﺧﺎل او اﺧﺮاج

.

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٧٦

The OR instruction produces a 1 in the destination for each bit position in which

either or both operands contain 1. OR is generally used to force specific bits to 1. For

example:

ﺎز"""ﻌﯾا نا

OR

ﺪ"""ﻟﻮﯾ

1

ﻰ"""ﻠﻋ يﻮ"""ﺘﺤﯾ تﺎ"""ﻧﺎﯿﺒﻟا ﻞ"""ﻣﺎﻌﻤﻟ ﻦﯿ"""ﺘﺒﻟا ﻼ"""ﻛ وا ﺪ"""ﺣا نﻮ"""ﻛ ﺔ"""ﻟﺎﺣ ﻲ"""ﻓ ﺖ"""ﺑ ﻊ"""ﻗﻮﻣ ﻞ"""ﻜﻟ ﺮﻘﺘ"""ﺴﻤﻟا ﻲ"""ﻓ

1

وھﻮ ﺑﺸﻜﻞ ﻋﺎم ﯾﺴﺘﺨﺪم ﻻﺟﺒﺎر ﻣﻮاﻗﻊ ﺑﺘﺎت ﻣﻌﯿﻨﺔ ان ﺗﻜﻮن واﺣﺪ وﻛﻤﺜﺎل،

OR BX,0C000H

sets the two most-significant bits (14 and 15) of BX to 1 and leaves all other bits

unchanged.

ﻮف"""ﺳ ﻖﺑﺎ"""ﺴﻟا زﺎ"""ﻌﯾﻻا نا

ﺔ"""ﻤﯿﻗ ﻞ"""ﻌﺠﯾ

ﺔ"""ﻤﯿﻗ ﻰ"""ﻠﻋﻻا ﻦﯿ"""ﺘﺒﻟا

(14 and 15)

ﺠﻞ"""ﺴﻤﻟ

BX

ﺎت"""ﺘﺒﻟا ﻲﻗﺎ"""ﺑ كﺮ"""ﺘﯾو ﺪ"""ﺣاو

ﺑﺪون ﺗﻐﯿﯿﺮ

.

The XOR instruction can be used to determine which bits differ between two

operands or to reverse the settings of selected bits. XOR puts a 1 in the destination for

every bit position in which the operands differ (one operand has 0 and the other has

1). If both operand's bits are either 0 or 1, XOR clears the destination bit to 0. For

example:

ﺎز"""ﻌﯾﻻ ﻦ"""ﻜﻤﯾ

XOR

ﻮم"""ﻘﯾ ﺚ"""ﯿﺣ ، ةدﺪ"""ﺤﻤﻟا تﺎ"""ﺘﺒﻟا ﺔ"""ﻤﯿﻗ ﺲ"""ﻜﻌﻟ وا تﺎ"""ﻧﺎﯿﺑ ﻞ"""ﻣﺎﻌﻣ ﻦﻤ"""ﺿ ﺔ"""ﻔﻠﺘﺨﻣ ﻦﯿ"""ﺘﺑ يا دﺪ"""ﺤﯾ نا

XOR

ﺔ"""ﻔﻠﺘﺨﻣ تﺎ"""ﻧﺎﯿﺒﻟا ﻲﻠﻣﺎ"""ﻌﻣ تﺎ"""ﺘﺑ نﻮ"""ﻜﺗ ﺎﻣﺪ"""ﻨﻋ ﺮﻘﺘ"""ﺴﻤﻟا ﻲ"""ﻓ ﺖ"""ﺒﻟا ﻊ"""ﻗﻮﻣ ﻲ"""ﻓ ﺪ"""ﺣاو ﻊ"""ﺿﻮﺑ

)

ﻰ"""ﻠﻋ يﻮ"""ﺘﺤﯾ ﺎﻤھﺪ"""ﺣا

ﺪ"""ﺣاو ﻰ"""ﻠﻋ ﻲﻧﺎ"""ﺜﻟاو ﻒ"""ﺼﻟا

(

"""ﺎ واﺣ"""ﻤھﻼﻛ ﻦﯿﮭﺑﺎ"""ﺸﺘﻣ ﻦﯿ"""ﺘﺒﻟا نﻮ"""ﻛ ﺔ"""ﻟﺎﺣ ﻲ"""ﻓو ،

ﺖ"""ﺑ ﺮﻔ"""ﺼﯾ فﻮ"""ﺳ زﺎ"""ﻌﯾا نﺎ"""ﻓ ﺮﻔ"""ﺻ وا ﺪ

اﻟﻤﺴﺘﻘﺮ وﻛﻤﺜﺎل

:

XOR BX,0C000H

reverses the state of the two most-significant bits of BX (14 and 15) and leaves all

other bits as they were.

ﺣﯿﺚ ﯾﻘﻮم اﻻﯾﻌﺎز اﻟﺴﺎﺑﻖ ﺑﻌﻜﺲ اﻟﺒﺘﯿﻦ ذوي اﻟﻘﯿﻤﺔ اﻟﻌﻠﯿﺎ ﻟﻤﺴﺠﻞ

BX

وﯾﺘﺮك

ﺑﺎﻗﻲ اﻟﺒﺘﺎت ﻋﻠﻰ ﺣﺎﻟﮭﺎ

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٨٦

Logical NOT (NOT)

The NOT instruction reverses the state of each bit in a register or memory operand

without affecting any flags. That is, NOT changes each 1 to 0 and each 0 to 1. In other

words, it takes the one's-complement of an operand.

ﯾﻘﻮم اﯾﻌﺎز

NOT

ﺑﻌﻜﺲ ﺣﺎﻟﺔ ﻛﻞ ﺑﺖ ﻣﻮﺟﻮد ﻓﻲ ﻣﺴﺠﻞ او ﻣﻮﻗﻊ ذاﻛﺮة ﻟﻤﻌﺎﻣﻞ ﺑﯿﺎﻧﺎت ﺑﺪون اﻟﺘﺎﺛﯿﺮ ﻋﻠﻰ

flags

وھﺬا ﯾﻌﻨﻲ ان

ﺎز"ﻌﯾا

NOT

ﺬ"ﺧﺎﺑ مﻮ""ﻘﯾ ﮫ""ﻧﺎﻓ ىﺮ""ﺧا ةرﺎ"ﺒﻌﺑو ﺪ""ﺣاو ﻰ""ﻟا ﺮﻔ"ﺻ ﻞ""ﻛو ﺮﻔ""ﺻ ﻰ""ﻟا ﺪ"ﺣاو ﻞ""ﻛ ﺮ""ﯿﻐﯾ

1's complement

ﻞ""ﻣﺎﻌﻤﻟ

اﻟﺒﯿﺎﻧﺎت

.

Test (TEST)

The TEST instruction ANDs two operands, but affects only the flags; it doesn't alter

either operand. TEST does the same as AND: it clears CF and OF to 0, updates PF,

ZF, and SF, and leaves AF undefined.

If you follow TEST with a JNZ (Jump If Not Zero) instruction, that makes the jump

if there are any corresponding 1 bits in both operands.

ﺎز""""ﻌﯾا نا

TEST

ﻞ""""ﻤﻌﺑ مﻮ""""ﻘﯾ

AND

ﻰ""""ﻠﻋ ﻂ""""ﻘﻓ ﺮﺛﺆ""""ﯾ ﮫ""""ﻨﻜﻟو تﺎ""""ﻧﺎﯿﺑ ﻲﻠﻣﺎ""""ﻌﻤﻟ

Flags

ﺎﻣﻠﻲ""""ﻌﻣ ﻦ""""ﻣ يا ﺮ""""ﯿﻐﯾﻻو

اﻟﺒﯿ

ﺎ

ﻞ"""ﺜﻣ ﻞ"""ﻤﻌﯾ ﻲ"""ھو ﺎ"""ﮭﯿﻠﻋ ﻞ"""ﻤﻌﯾ ﻲ"""ﺘﻟا تﺎ"""ﻧ

AND

ﻦ"""ﻣ ﻞ"""ﻛ ﺮﻔ"""ﺼﯾ ﺚ"""ﯿﺣ

CF and OF

ﺪث"""ﺤﯾو

PF

و

ZF

و

SF

وﻻﯾﺆﺛﺮ ﻋﻠ

ﻰ

AF

.

ﺎز""ﻌﯾا ﺬ""ﯿﻔﻨﺗ ﻢ""ﺗ اذاو

JNZ (Jump If Not Zero)

ﺪ""ﻌﺑ

TEST

ﻊ""ﻗاﻮﻣ ﻦ""ﻣ يا نﺎ""ﻛ اذا ثﺪﺤﺘ""ﺳ ﺰ""ﻔﻘﻟا ﺔ""ﯿﻠﻤﻋ نﺎ""ﻓ

ﻣﻌﺎﻣﻠﻲ اﻟﺒﯿﺎﻧﺎت ﻋﻠﻰ واﺣﺪﯾﻦ

.

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٩٦

The summary of logical instructions in Table 4

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٠٧

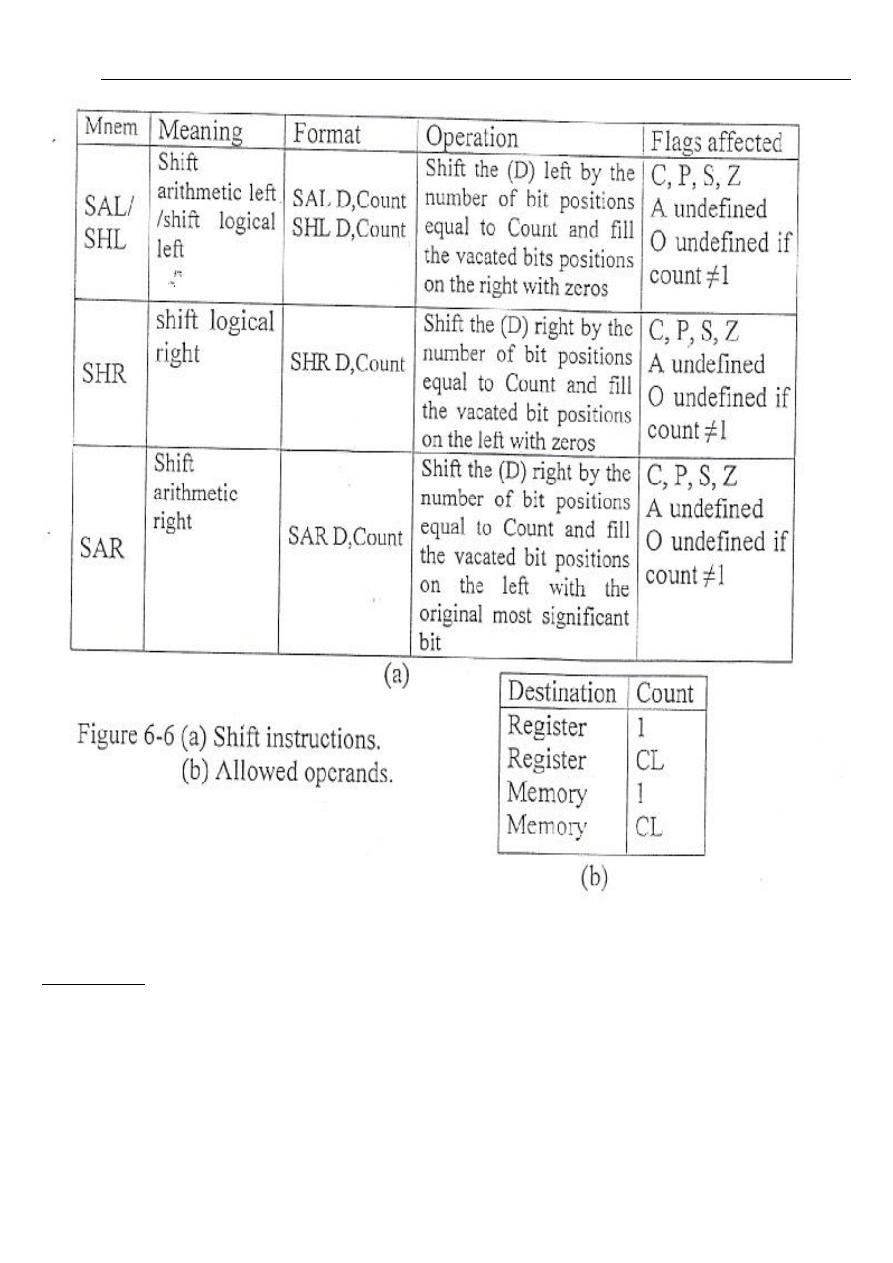

Shift instructions: Shift instructions can perform two basic types of shift operations; the

logical shift and the arithmetic shift. Also, each of these operations can be performed to

the right or to the left.

ﺎر او"ﺴﯿﻟا ﻰ"ﻟا ﻒ"ﯿﺣﺰﺘﻟا ﻢﺘ"ﯾ نا ﻦ"ﻜﻤﯾو ﻲ"ﺿﺎﯾﺮﻟا ﻒ"ﯿﺣﺰﺘﻟاو ﻲ"ﻘﻄﻨﻤﻟا ﻒ"ﯿﺣﺰﺘﻟا ﻮ"ھ ﻦﯿﻋﻮ"ﻨﺑ ﻒ"ﯿﺣﺰﺘﻟا تازﺎ"ﻌﯾا ﺬ"ﯿﻔﻨﺗ ﻦﻜﻤﯾ

اﻟﯿﻤﯿﻦ

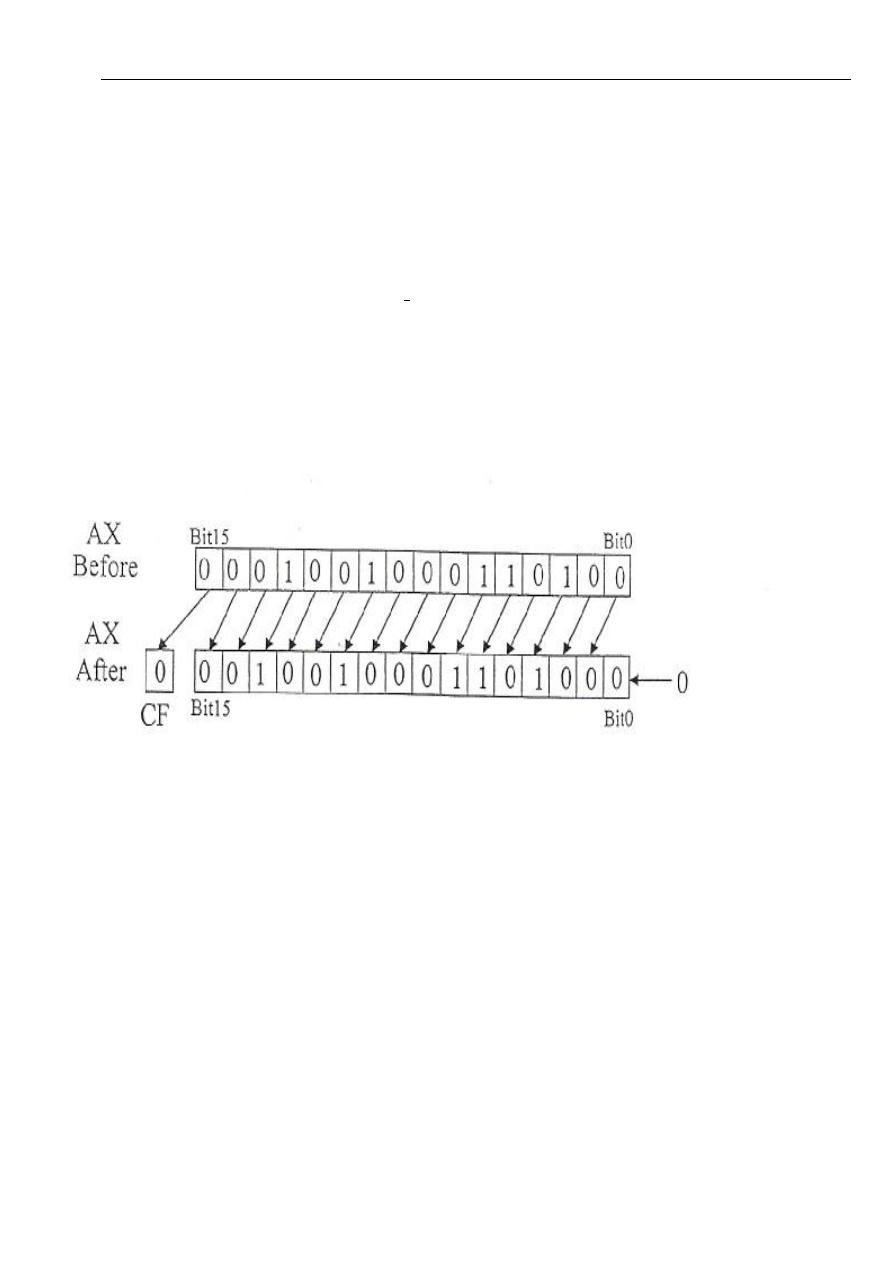

SHL, SHR, SAL, and, SAR instructions: The operation of these instructions is described

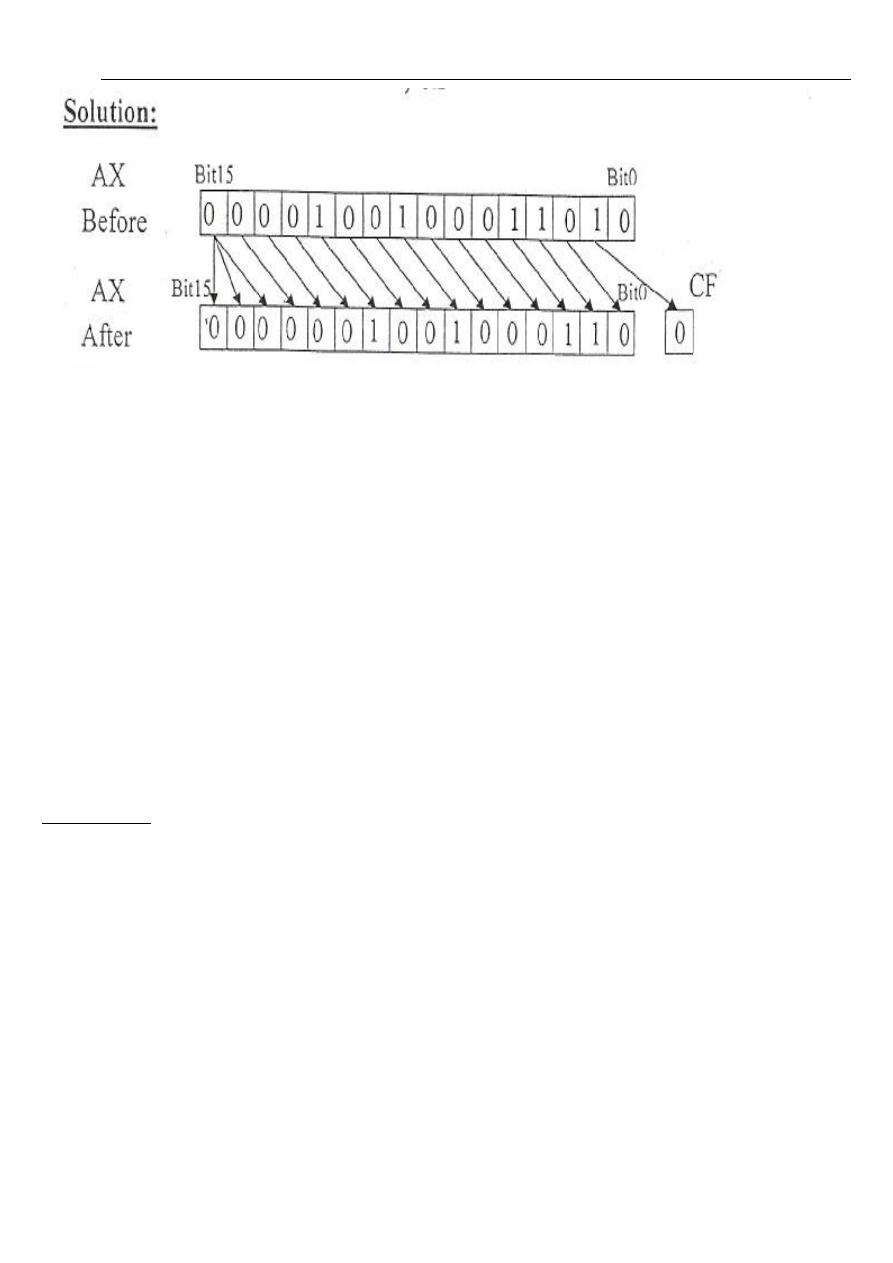

in figure 1. As an example if (AX)=1234H, Executing SHL AX,1 can be illustrated as

shown below:

وﯾﻤﻜﻦ وﺻﻒ ﻋﻤﻞ ھﺬه اﻻﯾﻌﺎزات ﻣﻦ ﺧﻼل اﻟﺸﻜﻞ رﻗﻢ واﺣﺪ وﻛﻤﺜﺎل

AX=1234 and execute SHL AX,1

The 16-bit contents of the AX register are shifted 1 bit position to the left. The vacated

LSB location is filled with zero and the bit shifted out of the MSB is saved in CF.

ﻒ ال""ﯿﺣﺰﺗ ﻢﺘ""ﯾ

٦١

ﺠﻞ""ﺴﻣ ﻦﻤ""ﺿ ةاﻮ""ﺘﺤﻤﻟا ﺖ""ﺑ

AX

ﺪ""ﺣاو ﻊ""ﻗﻮﻣ

ﺖ""ﺒﻟاو رﺎ""ﺴﯿﻟا ﻰ""ﻟا

ﻰ""ﻧدﻻا ﻊ""ﻗﻮﻤﻟا وذ

)

ﯿﻦ""ﻤﯿﻟا ﻦ""ﻣ ﺖ""ﺑ لوا

(

ﺎل""ﺧدا ﻢﺘ""ﯾ

0

ﮫ""ﯿﻓ

واﻟﺒﺖ اﻟﻤﺰﺣﻒ ﻣﻦ اﻟﺒﺖ ذو اﻟﻘﯿﻤﺔ اﻟﻌﻈﻤﻰ

)

اول ﺑﺖ ﻣﻦ اﻟﯿﺴﺎر

(

ﯾﺬھﺐ اﻟﻰ

CF

.

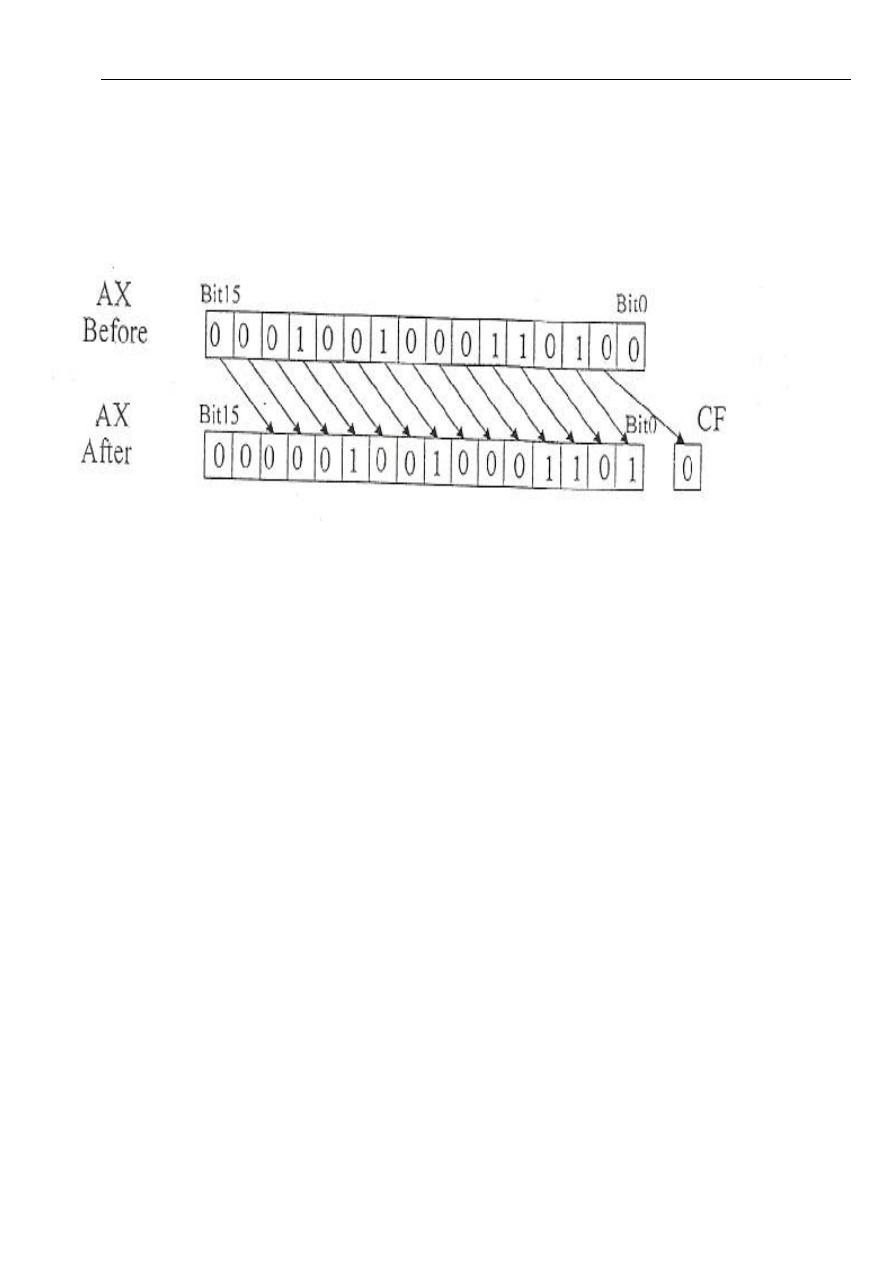

If the source operand is specified as CL instead of 1, the count in this register

represents the number of bit positions the contents of the operand are to be shifted. An

example of executing SHR AX, CL FOR (AX=1234H) and CL=2 is shown below:

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

١٧

ﺍﺫﺍﻜﺎﻥ ﻤﻌﺎﻤل ﺍﻟﻤﺼﺩﺭ

ﻗﺩ ﺘﻡ ﺘﺤﺩﻴﺩﻩ ﻓﻲ ﻤﺴﺠل

CL

ﻲـﺘﻟﺍ ﺕـﺒﻟﺍ ﻊـﻗﺍﻭﻤ ﺩﺩـﻋ لـﺜﻤﻴ لﺠـﺴﻤﻟﺍ ﺍﺫـﻫ ﻲﻓ ﺩﻌﻟﺍ ﻥﺎﻓ ، ﺩﺤﺍﻭﻟﺍ ﺔﻤﻴﻗ ﻥﻤ ﻻﺩﺒ

ﻭﻯ ﻭـﺘﺤﻤﻟﺍ ﻑـﻴﺤﺯﺘ ﺎﻫﺎﺴﺍ ﻰﻠﻋ ﻡﺘﻴﺴ

ﺎﺯـﻌﻴﻻﺍ ﺫﻔﻨﻨـﺴ لﺎـﺜﻤﻜ

SHR AX, CL

ﻴﻡـﻘﺒﻭ

(AX=1234H) and CL=2

ﺎـﻤﻜﻭ

ﻤﻭﻀﺢ ﻓﻲ ﺍﺩﻨﺎﻩ

:

In an arithmetic shift to the left, the SAL operation, the vacated bits at the right of the

operand are filled with zeros, whereas in an arithmetic shift to the right, the SAR

operation, the vacated bits at the left are filled with the value of the original MSB of the

operand.

ﻓﻲ ﺤﺎﻟﺔ ﺍﻟﺘﺯﺤﻴﻑ ﺍﻟﺭﻴﺎﻀﻲ ﻟﻠﻴﺴﺎﺭ ﻭﺘﻨﻔﻴﺫ ﻋﻤﻠﻴﺔ

SAL

ﻓﺎﻥ ﺍﻟﺒﺘﺎﺕ ﺍﻟﻔﺎﺭﻏﺔ ﺴﻭﻑ ﺘﻤﻠﻰﺀ ﺒﺎﺼﻔﺎﺭ

ﺒﻴﻨﻤﺎ ﻓﻲ ﺤﺎﻟﺔ

ﺍﻟﺘﺯﺤﻴﻑ ﺍﻟﺭﻴﺎﻀﻲ ﺍﻟﻰ ﺍﻟﻴﻤﻴﻥ ﻭﺘﻨﻔﻴﺫ ﻋﻤﻠﻴﺔ

SAR

ﻓﺎﻥ ﺍﻟﺒﺘﺎﺕ ﺍﻟ

ﺕ ﺫﻭـﺒﻟﺍ ﺔﻤﻴﻘﺒ ﺀﻰﻠﻤﺘ ﻑﻭﺴ ﺭﺎﺴﻴﻟﺍ ﻲﻓ ﺔﻏﺭﺎﻔ

اﻟﻌﻈﻤﻰ ﻟﻠﻤﻌﺎﻣﻞ اﻻﺻﻠﻲ

.

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٢٧

Example 1: If (CL) =02

16

and AX=091A

16

. Determine the new contents of AX and the

carry flag after executing the instruction

SAR AX, CL

Solution:

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٣٧

Rotate instructions: Rotate instructions, are similar to the shift instructions.

ﺗﺘﺸﺎﺑﮫ اﯾﻌﺎزات اﻟﺘﺪوﯾﺮ ﻣﻊ اﯾﻌﺎزات اﻟﺘﺰﺣﯿﻒ

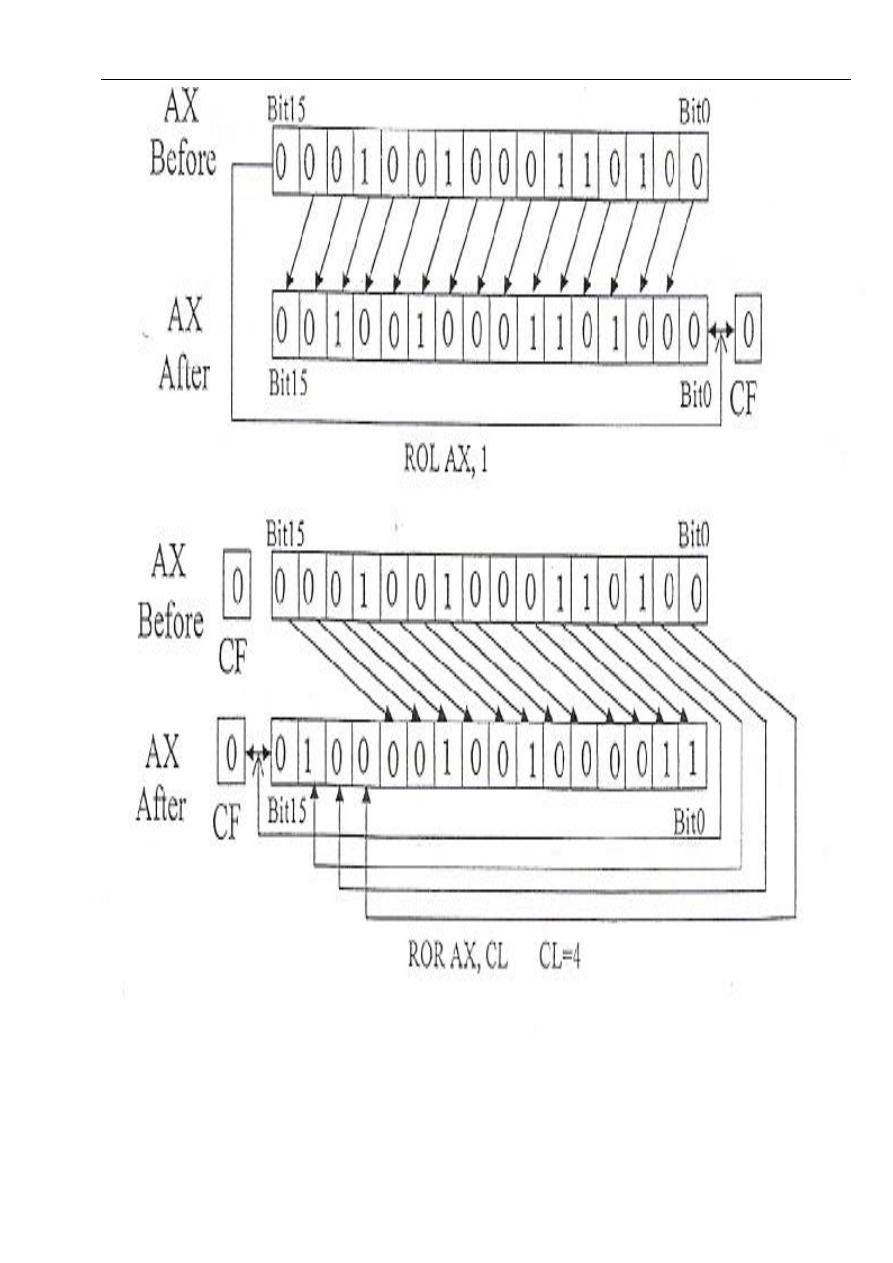

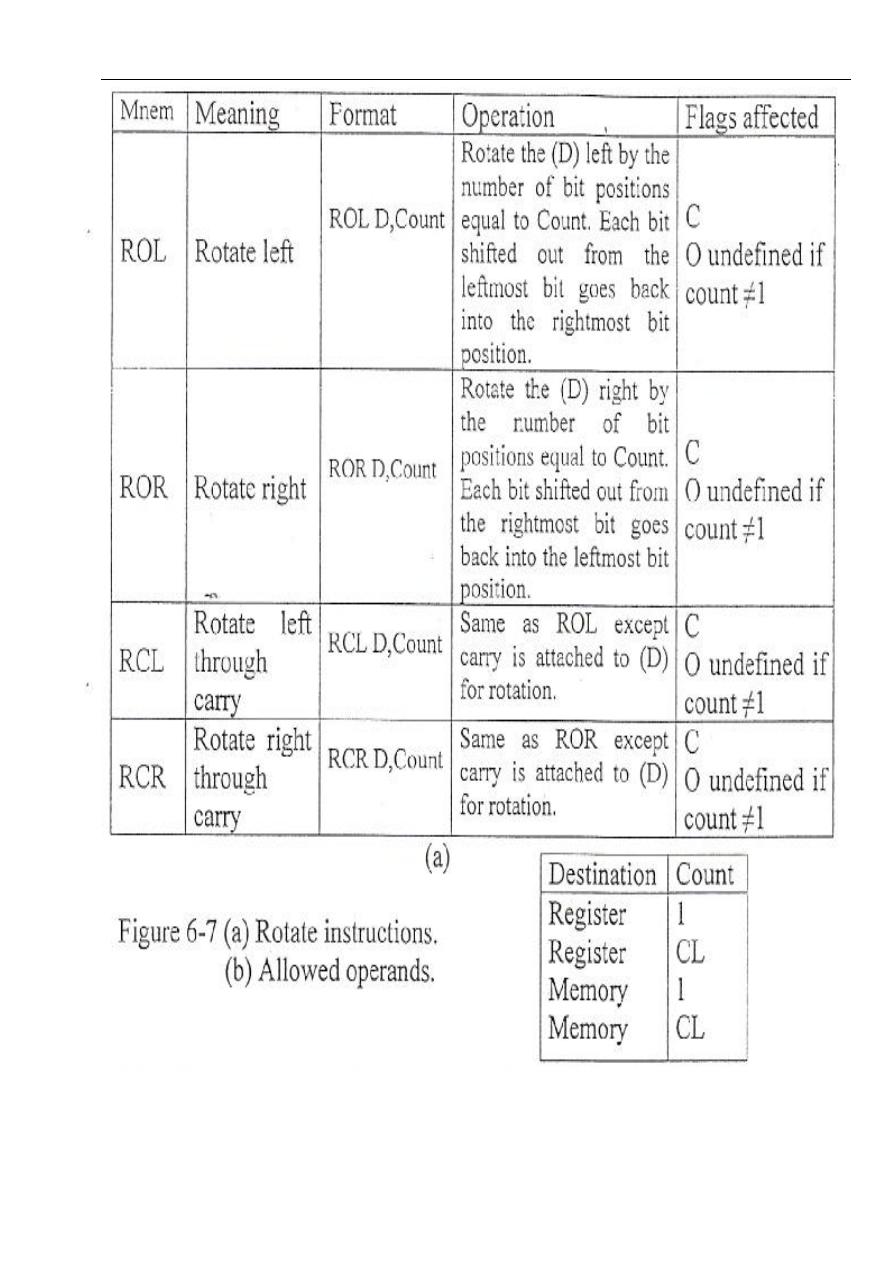

ROL, RQR, RCL, and, RCR instructions: The operation of these instructions is

described in figure 2. They have the ability to rotate the contents of either an internal

register or a storage location in memory. Also, the rotation that takes place can be

from 1 to 255 bit positions to the left or to the right. Moreover, in the case of a

multibit rotate, the number of bit positions to be rotated is specified by the value in

CL.

""ﯾﺒ

ﻜﻞ""ﺸﻟا ﻦﯿ

٢

ﺬ""ھ ﻞ""ﻤﻋ ﺔ""ﯿﻔﯿﻛ

ﺎزات""ﻌﯾﻻا ه

.

ﺮة""ﻛاذ ﻊ""ﻗﻮﻣ وا ﻲ""ﻠﺧاد ﻞﺠ""ﺴﻣ ىﻮ""ﺘﺤﻣ ﺮﯾوﺪ""ﺗ ﺔ""ﯿﻧﺎﻜﻣا ﺎ""ﮭﻟ تازﺎ""ﻌﯾﻻا هﺬ""ھو

ﻦ""ﻣ ﺮﯾوﺪ""ﺘﻟا تاﺮ""ﻣ دﺪ""ﻋ نﺎ""ﻓ ﻚﻟﺬ""ﻛو

1 to 255 bit

""ﯿﻦ وﻓ""ﻤﯿﻟاوا رﺎ""ﺴﯿﻟا ﻰ""ﻟا

ﻲ

ﺪد""ﻋ نﺎ""ﻓ ﺖ""ﺑ ﻦ""ﻣ ﺮ""ﺜﻛﻻ ﺮﯾوﺪ""ﺘﻟا ﺔ""ﻟﺎﺣ

اﻟﺒﺘﺎت ﺳﻮف ﺗﺤﺪد ﺣﺴﺐ ﻗﯿﻤﺔ ﻣﺴﺠﻞ

CL

.

Example 2: If (CL) =04

16

and AX=1234A

16

. Determine the new contents of AX and

the carry flag after executing the instructions:

a)ROL AX, 1

b)ROR AX, CL

SOLUTION:

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٤٧

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٥٧

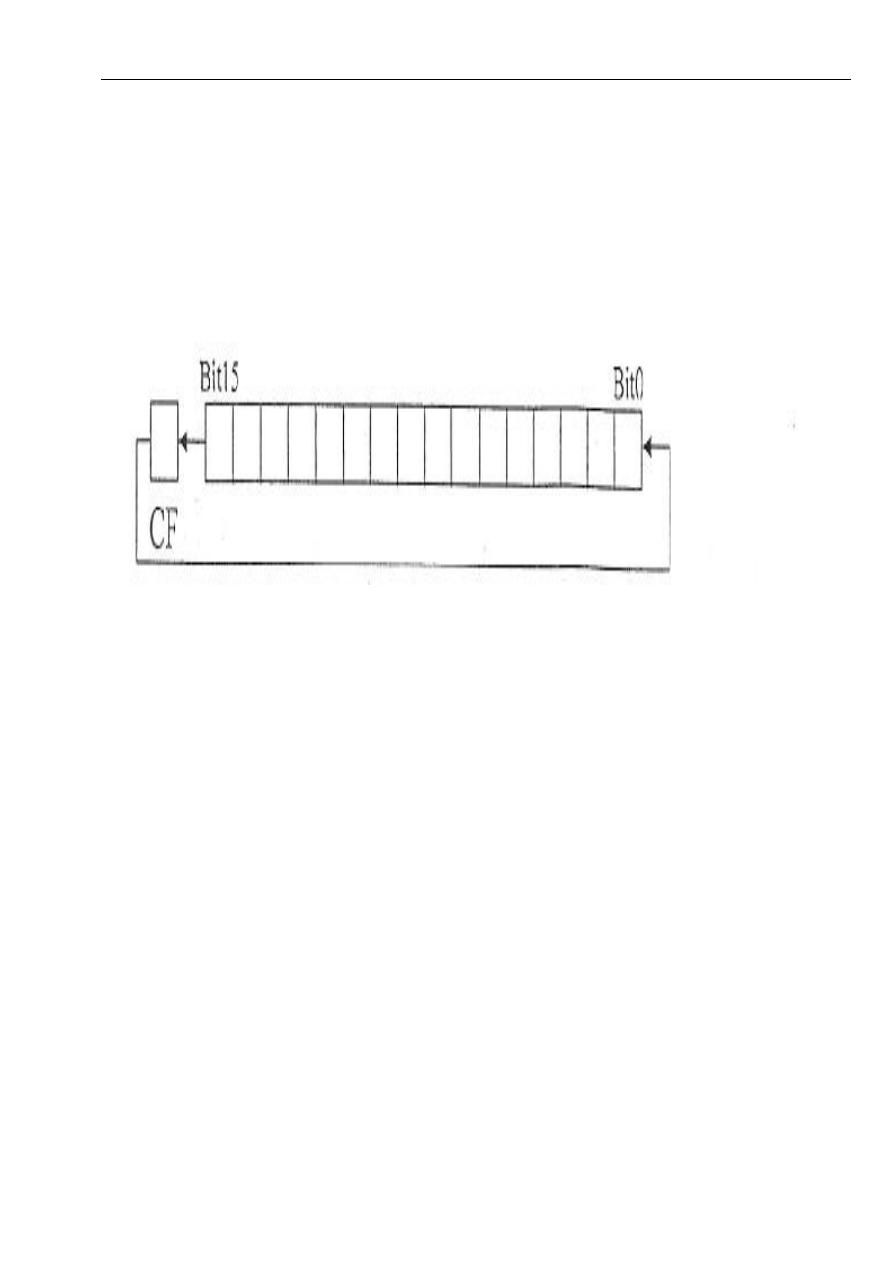

The other two rotate instructions, RCL and RCR, differ from ROL and ROR in that the bits are

rotated through the carry flag. The following figure illustrates the rotation that takes place due

to execution of the RCL instruction.

واﻻﯾﻌﺎزﯾﻦ اﻻﺧﺮﯾﯿﻦ ھﻤﺎ

RCL and RCR

واﻟﺘﻲ ﺗﺨﺘﻠﻒ ﻋﻦ

ROL and ROR

ﺑﺎن اﻟﺒﺘﺎت ﺗﺪور ﻣﻦ ﺧﻼل

CF

واﻟﺸﻜﻞ

ﻓﻲ ادﻧﺎه ﯾﺒﯿﻦ ﻛﯿﻔﯿﺔ ﺗﻨﻔﯿﺬ اﻻﯾﻌﺎز

RCL

.

ﺤﺎﺴﺒﺎﺕ ﻤﺘﻘﺩﻤﺔ ﺍﻟﻤﺭﺤﻠﺔ ﺍﻟﺜﺎﻟﺜﺔ ﻫﻨﺩﺴﺔ ﻜﻬﺭﻭ ﻤﻴﻜﺎﻨﻴﻙ ﺍﻟﻤﺩﺭﺱ ﻤﺴﺎﻋﺩ ﺍﻨﻤﺎﺭ ﺨﻠﻴل ﺍﺒﺭﺍﻫﻴﻡ

٦٧